# NPC

### OVERVIEW

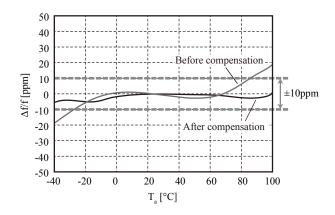

The 5043 series are high-stability clock oscillator ICs with built-in frequency adjustment functions. The frequency adjustment functions can be optimized, by the addition of a minimal adjustment process, to improve the frequency stability. The function is implemented using frequency adjustment data written to a built-in EEPROM over a 1-wire serial interface. The ICs are ideal for compact crystal oscillators for use in applications such as Wireless-LAN that require high frequency stability in the order of  $\pm 30$  to  $\pm 10$ ppm. They use a pad layout suitable for flip chip bonding mounting.

### FEATURES

- Realizing frequency stability improvement with minimal additional process

- Temperature compensation range / Operating temperature range: -40°C to +85°C

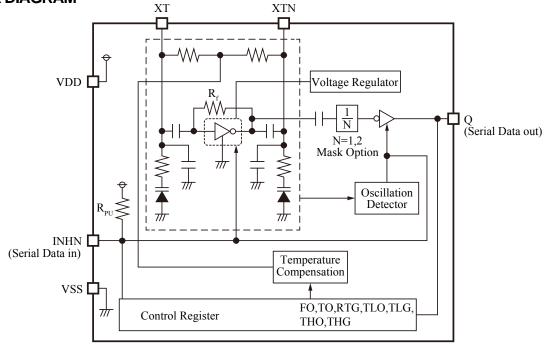

- · Frequency adjustment functions built-in

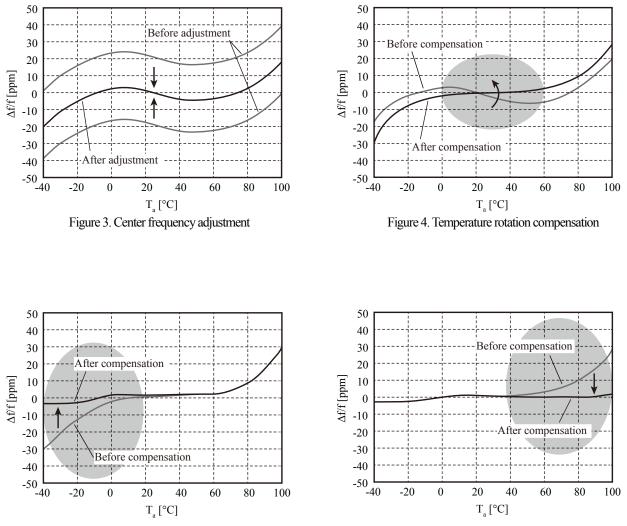

- <Frequency-temperature characteristics compensation function> AT-cut crystal, 3rd order frequency-temperature characteristics compensation, with independent low-temperature and hightemperature compensation settings

- Center frequency adjustment function

- Temperature rotation compensation function

- Low-temperature characteristics compensation

- High-temperature characteristics compensation

- Rewritable EEPROM built-in

- 6 pads: same as general clock oscillator ICs

- Operating supply voltage range: 2.25V to 3.63V

- Recommended oscillation frequency range

- (for fundamental oscillation): 20MHz to 55MHz

- Frequency divider built-in Selectable by version:  $f_0$ ,  $f_0/2$

- Standby function

- High-impedance in standby mode, oscillator stops

- CMOS output

- 15pF output load capacitance

- Pad layout for flip chip bonding

- Wafer form (WF5043AxB)

### SERIES CONFIGURATION

### FREQUENCY CHARACTERISTICS COMPENSATION BEFORE and AFTER ADJUSTMENT

### **APPLICATIONS**

- 3.2mm×2.5mm, 2.5mm×2.0mm, 2.0mm×1.6mm size miniature crystal oscillator modules

- Wireless-LAN and applications requiring high-stability clock oscillators

| Version name | Operating supply voltage<br>range [V] | Recommended oscillation<br>frequency range <sup>*1</sup> [MHz] | Output frequency  |  |

|--------------|---------------------------------------|----------------------------------------------------------------|-------------------|--|

| 5043A1B      | 2.25 to 3.63                          | 20 to 55                                                       | $f_0$             |  |

| 5043A2B      | 2.25 10 5.05                          | 2010 33                                                        | f <sub>0</sub> /2 |  |

\*1. The recommended oscillation frequency range is a yardstick value derived from the crystal used for NPC characteristics authentication. However, the recommended oscillation frequency range is not guaranteed. Specifically, the characteristics can vary greatly due to crystal characteristics and mounting conditions, so the oscillation characteristics of components must be carefully evaluated.

### **ORDERING INFORMATION**

| Device      | Package    | Version name         |  |  |  |

|-------------|------------|----------------------|--|--|--|

| WF5043AxB-4 | Wafer form | Form WF : Wafer form |  |  |  |

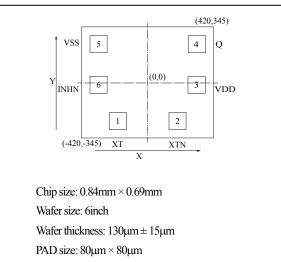

### PAD LAYOUT

(Unit: µm)

Chip base: V<sub>SS</sub> level

### **PIN DESCRIPTION and PAD COORDINATE**

| No. PIN | I/O <sup>*1</sup> | Description | PAD coordinate [µm]                                                                                                                  |        |        |

|---------|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 140.    | 1111              | 10          | Description                                                                                                                          | X      | Y      |

| 1       | XT                | Ι           | Crystal connection pins                                                                                                              | -225.2 | -253.5 |

| 2       | XTN               | 0           | Crystal is connected between XT and XTN.                                                                                             | 225.2  | -253.5 |

| 3       | VDD               | -           | (+) supply voltage                                                                                                                   | 328.5  | -5.0   |

| 4       | Q                 | 0           | Output pin (Output one of $f_0, f_0/2$ )                                                                                             | 328.5  | 223.8  |

| 5       | VSS               | -           | (-) ground                                                                                                                           | -328.5 | 223.8  |

| 6       | INHN              | Ι           | Input pin controlled output state (oscillator stops and output pin<br>becomes Hi-Z when LOW), power-saving pull-up resistor built-in | -328.5 | -5.0   |

\*1. I: Input pin O: Output pin

### **BLOCK DIAGRAM**

### SPECIFICATIONS

### Absolute Maximum Ratings

V<sub>SS</sub>=0V

| Parameter                                            | Symbol              | Condition            | Rating                       | Unit  |

|------------------------------------------------------|---------------------|----------------------|------------------------------|-------|

| Supply voltage range <sup>*1</sup>                   | V <sub>DD</sub>     | Between VDD and VSS  | -0.3 to +4.0                 | V     |

| Program read/write input voltage range <sup>*1</sup> | $V_{PP}$            | Between INHN and VSS | -0.3 to +16.5                | V     |

| Input voltage range <sup>*1*2</sup>                  | $V_{\mathbb{I}\!N}$ | Input pins           | -0.3 to V <sub>DD</sub> +0.3 | V     |

| Output voltage range <sup>*1*2</sup>                 | V <sub>OUT</sub>    | Output pins          | -0.3 to V <sub>DD</sub> +0.3 | V     |

| Output current <sup>*1</sup>                         | I <sub>OUT</sub>    | Q pin                | ±20                          | mA    |

| Storage temperature range <sup>*3</sup>              | T <sub>STG</sub>    | Wafer form           | -65 to +150                  | °C    |

| EEPROM maximum writes                                | N <sub>EW</sub>     |                      | 100                          | times |

\*1. This parameter rating is the values that must never exceed even for a moment. This product may suffer breakdown if this parameter rating is exceeded. Operation and characteristics are guaranteed only when the product is operated at recommended operating conditions.

\*2.  $V_{DD}$  is a  $V_{DD}$  value of recommended operating conditions.

\*3. When stored in nitrogen or vacuum atmosphere applied to IC itself only (excluding packaging materials).

### **Recommended Operating Conditions**

$V_{SS}=0V$

| Parameter                           | Symbol           | Condition                         | Rating          |     |                 | Unit |  |

|-------------------------------------|------------------|-----------------------------------|-----------------|-----|-----------------|------|--|

|                                     |                  |                                   | MIN             | ТҮР | MAX             | Um   |  |

| Supply voltage                      | V <sub>DD</sub>  | Between VDD and VSS <sup>*2</sup> | 2.25            |     | 3.63            | V    |  |

| Input voltage                       | $V_{\mathbb{N}}$ | Input pins (XT, INHN)             | V <sub>SS</sub> |     | V <sub>DD</sub> | V    |  |

| Operating temperature               | Ta               |                                   | -40             |     | +85             | °C   |  |

| Oscillation frequency <sup>*1</sup> | $f_0$            |                                   | 20              |     | 55              | MHz  |  |

| Output frequency                    | f <sub>OUT</sub> | Q pin                             | 10              |     | 55              | MHz  |  |

| Output load capacitance             | CLOUT            | Q pin                             |                 |     | 15              | pF   |  |

\*1. The oscillation frequency is a yardstick value derived from the crystal used for NPC characteristics authentication. However, the oscillation frequency range is not guaranteed. Specifically, the characteristics can vary greatly due to crystal characteristics and mounting conditions, so the oscillation characteristics of components must be carefully evaluated.

\*2. Mount a ceramic chip capacitor that is larger than 0.01µF proximal to IC (within approximately 3mm) between VDD and VSS in order to obtain stable operation of 5043 series. In addition, the wiring pattern between IC and capacitor should be as wide as possible.

Note. Since it may influence the reliability if it is used out of range of recommended operating conditions, this product should be used within this range.

## Electrical Characteristics DC Characteristics

| <b>D</b> (                                  | G 1 1            | Condition                                                            |                         | Rating               |     |                    | TL.4 |

|---------------------------------------------|------------------|----------------------------------------------------------------------|-------------------------|----------------------|-----|--------------------|------|

| Parameter                                   | Symbol           |                                                                      |                         | MIN                  | ТҮР | MAX                | Unit |

| Operating current consumption <sup>*1</sup> |                  | $5043A1B(f_{OUT}=f_0)$                                               | V <sub>DD</sub> =2.5V   |                      | 1.4 | 2.8                |      |

|                                             | I <sub>DD</sub>  | measurement circuit 1, no load<br>INHN="HIGH", f <sub>0</sub> =48MHz | V <sub>DD</sub> =3.3V   |                      | 1.7 | 3.4                | mA   |

| operating current consumption               | IDD              | $5043A2B(f_{OUT}=f_0/2)$                                             | V <sub>DD</sub> =2.5V   |                      | 1.1 | 2.2                |      |

|                                             |                  | measurement circuit 1, no load<br>INHN="HIGH", f <sub>0</sub> =48MHz | V <sub>DD</sub> =3.3V   |                      | 1.4 | 2.7                | mA   |

| Standby current                             | I <sub>ST</sub>  | measurement circuit 1, INHN="LOW"                                    |                         |                      |     | 10                 | μΑ   |

| HIGH-level output voltage                   | V <sub>OH</sub>  | measurement circuit 3, Q pin, I <sub>OH</sub> =-4mA                  |                         | V <sub>DD</sub> -0.4 |     |                    | V    |

| LOW-level output voltage                    | V <sub>OL</sub>  | measurement circuit 3, Q pin, I <sub>OL</sub> =4                     | lmA                     |                      |     | 0.4                | V    |

| Output leakage current                      | т                | measurement circuit 4                                                | Q=V <sub>DD</sub>       |                      |     | 10                 |      |

|                                             | $I_Z$            | INHN="LOW"                                                           | Q=V <sub>SS</sub>       | -10                  |     |                    | μA   |

| HIGH-level input voltage                    | $V_{I\!H}$       | measurement circuit 5, INHN pin                                      |                         | $0.7V_{DD}$          |     |                    | V    |

| LOW-level input voltage                     | V <sub>IL</sub>  | measurement circuit 5, INHN pin                                      |                         |                      |     | 0.3V <sub>DD</sub> | V    |

| INHN pull-up resistance                     | R <sub>PU1</sub> | maaguramant airauit (                                                | INHN=V <sub>SS</sub>    | 0.4                  | 1.5 | 10                 | MΩ   |

|                                             | R <sub>PU2</sub> | measurement circuit 6                                                | INHN=0.7V <sub>DD</sub> | 50                   | 100 | 200                | kΩ   |

$V_{DD}$ =2.25 to 3.63V,  $V_{SS}$ =0V,  $T_a$ = -40 to +85°C,  $C_{LOUT}$ =15pF unless otherwise noted.

\*1. The consumption current I<sub>DD</sub>(C<sub>LOUT</sub>) with a load capacitance(C<sub>LOUT</sub>) connected to the Q pin is given by the following equation, where I<sub>DD</sub> is the no load consumption current and f<sub>OUT</sub> is the output frequency.

$I_{DD}(C_{LOUT})[mA] = I_{DD}[mA] + C_{LOUT}[pF] \times V_{DD}[V] \times f_{OUT}[MHz] \times 10^{-3}$

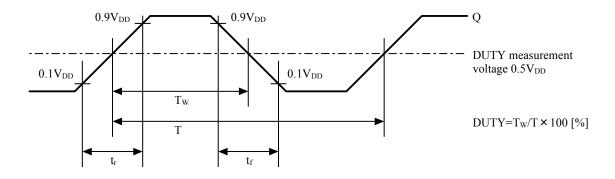

### AC Characteristics Clock Output Characteristics (Q pin)

| Parameter                 | Symbol          | Condition                                                                         |     | Unit |     |      |

|---------------------------|-----------------|-----------------------------------------------------------------------------------|-----|------|-----|------|

|                           |                 | Condition                                                                         | MIN | ТҮР  | MAX | Unit |

| Output duty cycle*1       | DUTY            | measurement circuit 1, threshold voltage $0.5V_{DD}$<br>DUTY = $T_W/T \times 100$ | 45  | 50   | 55  | %    |

| Rise time                 | t <sub>r</sub>  | measurement circuit 1, $0.1V_{DD} \rightarrow 0.9V_{DD}$                          |     |      | 4.5 | ns   |

| Fall time                 | t <sub>f</sub>  | measurement circuit 1, $0.9V_{DD} \rightarrow 0.1V_{DD}$                          |     |      | 4.5 | ns   |

| Output disable delay time | t <sub>OD</sub> | measurement circuit 2 <sup>*2</sup> , INHN= "HIGH"→"LOW"                          |     |      | 100 | ns   |

$V_{DD}=2.25$  to 3.63V,  $V_{SS}=0V$ ,  $T_a=-40$  to +85°C,  $C_{LOUT}=15$ pF unless otherwise noted.

\*1. This parameter is measured using the NPC's standard crystal. Note that the values will vary with the crystal characteristics used or mounting conditions.

\*2. Measurement circuit 2 takes an external input on the XT pin, without using a crystal.

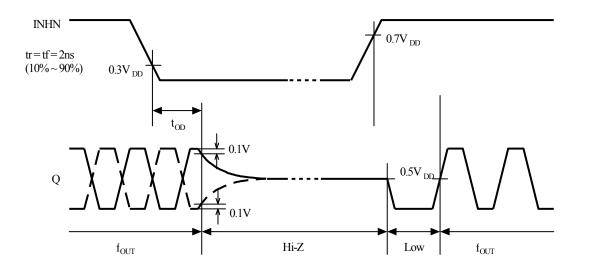

Figure 1. Output switching waveform

Figure 2. Output disable timing chart

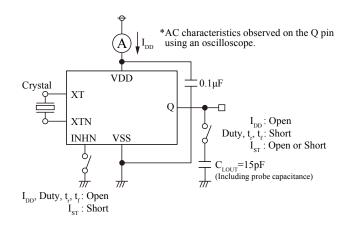

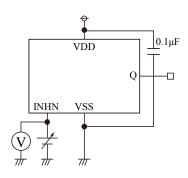

### MEASUREMENT CIRCUITS MEASUREMENT CIRCUIT 1

Measurement Parameter: I<sub>DD</sub>, I<sub>ST</sub>, DUTY, t<sub>r</sub>, t<sub>f</sub>

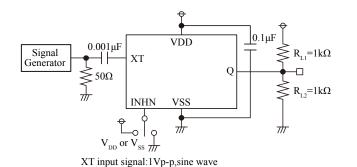

### **MEASUREMENT CIRCUIT 2**

Measurement Parameter:  $t_{\text{OD}}$

VDD

VSS

$\overline{H}$

он

Q

0.1µF

V V<sup>OH</sup>

OI

$(\mathbf{V})$

$\frac{1}{2}$

ΔV

$\Delta V=50 \times I_{_{OL}}$

Q

50Ω

w

$0.1 \mu F$

$\frac{1}{2}$

V<sub>ol</sub>

$\frac{1}{2}$

### **MEASUREMENT CIRCUIT 3**

0.001µF

ΗĤ

\$50Ω m

٨

$\Delta V=50 \times I_{_{OH}}$

XT

XT input signal:1Vp-p,sine wave

Signal

Generator

Q

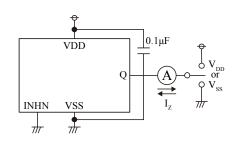

Measurement Parameter:  $V_{OH}$ ,  $V_{OL}$

Measurement Parameter: Iz

### **MEASUREMENT CIRCUIT 5**

Measurement Parameter:  $V_{I\!H\!},V_{I\!L}$

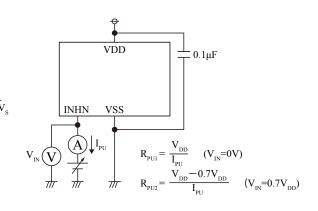

### **MEASUREMENT CIRCUIT 6**

Measurement Parameter:  $R_{PU1}, R_{PU2}$

### FUNCTIONAL DESCRIPTION Frequency Adjustment Function

The 5043 series ICs have a built-in oscillator frequency adjustment function. The frequency adjustment settings are written to and stored in internal EEPROM, making the devices easy to setup. A typical compensation sequence is shown below.

Figure 5. Low-temperature characteristics compensation

Figure 6. High-temperature characteristics compensation

### **Power-saving Pull-up Resistor**

The INHN pin pull-up resistance changes its value to R<sub>PU1</sub> or R<sub>PU2</sub> in response to the input level (OPEN, HIGH or LOW).

When INHN is tied to LOW level, the pull-up resistance becomes large ( $R_{PU1}$ ), thus reducing the current consumed by the resistance. When INHN is left open circuit or tied to HIGH level, the pull-up resistance becomes small ( $R_{PU2}$ ), thus internal circuit of INHN becomes HIGH level.

Consequently, the IC is less susceptible to the effects of noise, helping to avoid problems such as the output stopping suddenly.

### **Oscillation Detection Function**

The 5043 series have an oscillation detection circuit.

The oscillation detection circuit disables the output until crystal oscillation becomes stable when oscillation circuit starts up. This function avoids the abnormal oscillation in the initial power up and in a reactivation by INHN.

### USAGE NOTES

### **Consideration for Mounting IC**

Mount a ceramic chip capacitor that is larger than  $0.01\mu$ F proximal to IC (within approximately 3mm) between VDD and VSS in order to obtain stable operation of 5043 series. In addition, the wiring pattern between IC and capacitor should be as wide as possible.

Please pay your attention to the following points at time of using the products shown in this document.

1. The products shown in this document (hereinafter "Products") are designed and manufactured to the generally accepted standards of reliability as expected for use in general electronic and electrical equipment, such as personal equipment, machine tools and measurement equipment. The Products are not designed and manufactured to be used in any other special equipment requiring extremely high level of reliability and safety, such as aerospace equipment, nuclear power control equipment, medical equipment, transportation equipment, disaster prevention equipment, security equipment. The Products are not designed and manufactured to be used for the apparatus that exerts harmful influence on the human lives due to the defects, failure or malfunction of the Products. If you wish to use the Products in that apparatus, please contact our sales section in advance.

In the event that the Products are used in such apparatus without our prior approval, we assume no responsibility whatsoever for any damages resulting from the use of that apparatus.

- 2. NPC reserves the right to change the specifications of the Products in order to improve the characteristics or reliability thereof.

- 3. The information described in this document is presented only as a guide for using the Products. No responsibility is assumed by us for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of the third parties. Then, we assume no responsibility whatsoever for any damages resulting from that infringements.

- 4. The constant of each circuit shown in this document is described as an example, and it is not guaranteed about its value of the mass production products.

- 5. In the case of that the Products in this document falls under the foreign exchange and foreign trade control law or other applicable laws and regulations, approval of the export to be based on those laws and regulations are necessary. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

SEIKO NPC CORPORATION

1-9-9, Hatchobori, Chuo-ku, Tokyo 104-0032, Japan Telephone: +81-3-5541-6501 Facsimile: +81-3-5541-6510 http://www.npc.co.jp/ Email:sales@npc.co.jp

ND12041-E-00 2012.12